# Full Subtractor Design of Energy Efficient, Low Power Dissipation Using GDI Technique

M. CHAITANYA SRAVANTHI<sup>1</sup>, G. RAJESH<sup>2</sup>

<sup>1</sup>PG Scholar, Dept of ECE, Vemu Institute of Technology, Chittoor, AP, India. <sup>2</sup>Assistant Professor, Dept of ECE, Vemu Institute of Technology, Chittoor, AP, India.

**Abstract:** This paper proposes the design of an energy efficient, high speed and low power full subtractor using Gate Diffusion Input (GDI) technique. The entire design has been performed in 150nm technology and on comparison with a full subtractor employing the conventional CMOS transistors, transmission gates and Complementary Pass-Transistor Logic (CPL), respectively it has been found that there is a considerable amount of reduction in Average Power consumption (Pavg), delay time as well as Power Delay Product (PDP). Pavg is as low as 13.96nW while the delay time is found to be 18.02pico second thereby giving a PDP as low as 2.51x10-19 Joule for 1 volt power supply. In addition to this there is a significant reduction in transistor count compared to traditional full subtractor employing CMOS transistors, transmission gates and CPL, accordingly implying minimization of area. The simulation of the proposed design has been carried out in Tanner SPICE and the layout has been designed in Microwind.

Keywords: FIR Filter, Error Correction Code, Brent Kung Adder (BKA), Vedic Multiplier.

# I. INTRODUCTION

A subtractor is one of the significant building blocks in the construction of a binary divider . In ecent times, applications are aimed at battery operated devices so that power dissipation becomes one of the primary design constraints [3]–[10]. In the past processor speed, circuit speed, area, performance, cost and reliability were of prime importance. Power consumption was of secondary concern. However, in recent years power consumption is being given equal importance. The reason for such a changing trend is attributed probably due to the rapid increase in portable computing devices and wireless systems which demand communication high speed computations and complex functionality with low power consumption. In addition to this high performance processors consume severe power which in turn increases the cost associated with packaging and cooling. Subsequently there is a rise in the power density of VLSI chips thereby disturbing the reliability. It has been found that every 100 rise in operating temperature roughly doubles the failure rate of components made up of Silicon due to several Silicon failure mechanisms such as thermal runaway, junction diffusion, electro migration diffusion, electrical parameter shift, package related failure and Silicon interconnect failure [11]. From the environment point of view, the lesser the power dissipation of electronic components, lesser will be the heat dissipated in rooms which in turn will have a positive impact on the global environment.

Also, lesser electricity will be consumed. Therefore, for further optimization of performance of a full subtractor in terms of power consumption, delay time as well as Power Delay Product (PDP), a new low power, high speed energy efficient full subtractor is being proposed using Gate Diffusion Input (GDI) technique. GDI is a novel modus operandi for low power digital circuits. This procedure allows reduction in power consumption, propagation delay and transistor count of digital circuit. The method can be used to minimize the number of transistors compared to conventional Complementary Pass-transistor Logic (CPL) and Dual Pass transistor Logic (DPL) CMOS design. The proposed subtractor has a transistor count of 14 a reduction of 72.00%, 63.16% and 58.82% compared to a full subtractor composed of CMOS logic, transmission gates and CPL, proposing a reduction in area. In order to establish the technology independence of the design the proposed subtractor has been simulated using 150nm technology.

# **II. GATE DIFFUSION INPUT (GDI)**

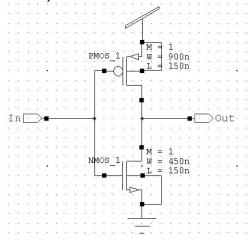

Gate Diffusion Input (GDI) method is based on the utilization of a simple cell as shown in Fig. 1 which can be used for low power digital circuits [3]. This technique is implemented in twin-well CMOS or Silicon on Insulator (SOI) technologies. In this process, the bulks of both NMOS and PMOS transistors are hardwired to their diffusions to reduce the bulk effect that is dependence of threshold voltage on source-to-bulk voltage [12]. The dependence of transistor threshold voltage on source-to-bulk voltage is as follows:

$$V_{th} = V_{th0} + \gamma \left( \sqrt{|2\phi_F + V_{SB}|} - \sqrt{|2\phi_F|} \right) - \eta V_{DS}$$

(1)

Where VSB is source-body voltage, Vth0 is threshold voltage at VSB=0,  $\gamma$  is linearized body coefficient,  $\Phi$ F is the Fermi potential and  $\eta$  is Drain nduced Barrier Lowering (DIBL) coefficient. Using this procedure power consumption can be reduced along with delay time thereby delivering a reduced power delay product. Consequently area of the circuit is minimized.

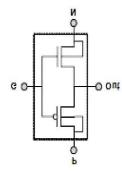

# Fig.1.Basic GDI Cell.

It should be noted that though the circuit resembles with standard CMOS inverter, there are certain important differences compared to conventional one. The GDI cell contains 3 inputs- P which is the input to the outer diffusion node of the PMOS transistor is not connected to V<sub>dd</sub> while N which is the input to the outer diffusion node of the NMOS transistor is not connected to GND, and G which is the common gate input of both the NMOS and PMOS transistors. The Out node which is the common diffusion of both the transistors may be utilized as input or output port depending on the circuit configuration. The ports P and N delivers 2 extra pins which yield the GDI design more compliant than the usual CMOS design [3]. Fig. 2 shows the transient response of a GDI cell which is quite similar to that of a standard CMOS inverter [13], [14]. This analysis is based on the Shockley model in which the drain current ID is represented as shown below

$$I_{D} = \begin{cases} I_{D0} \left( \frac{W}{L} \right) \, \ell! Q'S_{GS}(KT) \\ V_{GS} \leq V_{TH} : \text{subtreshold region} \\ K \left\{ (W_{GS} - V_{TH}) \, V_{DS} - 0.5 V_{DS}^{2} \right\} \\ (V_{DS} < V_{GS} - V_{TH} : \text{linear region} \\ 0.5 K \left( V_{GS} - V_{TH} \right)^{2} \\ (V_{DS} \geq V_{GS} - V_{TH} : \text{subtrain region} ) \end{cases}$$

Where K denotes device trans conductance parameter, VTH denotes threshold voltage, W denotes channel width and L denotes channel length.

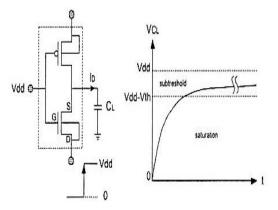

#### Fig.2. Transient response of a GDI cell.

However, it is to be mentioned that in GDI cell  $V_{ds}$  has to be considered as a variable of input voltage in Shockley model [3] in contrast with CMOS inverter analysis [15] where  $V_{gs}$  was considered as an input voltage.

# III. LOGIC GATES BASED ON GDI METHOD

Table I shows the various operations that can be performed with a basic GDI cell.

| TABLE I: Different Operatio | ons of Basic GDI Cell |

|-----------------------------|-----------------------|

|-----------------------------|-----------------------|

| N   | P           | G | Out   | Operation |

|-----|-------------|---|-------|-----------|

| ·0' | В           | A | ĀB    | Fl        |

| В   | T           | A | Ā+B   | F2        |

| "1" | В           | A | A+B   | OR        |

| В   | <b>'</b> 0' | A | AB    | AND       |

| C   | В           | A | ĀB+AC | MUX       |

| ·0' | ʻľ          | A | Ă     | NOT       |

From table I, it can be noticed that using only 2 transistors various functions can be performed. For instance, OR gate can be designed using a single GDI cell whereas in case of designing of an OR gate gate can be designed using only 2 transistors and even a Multiplexer MUX) can be devised using a single GDI cell. Thus, a simple alteration to the input configuration of the GDI cell would yield myriad variety of Boolean functions. Multiple-input gates can be implemented by combining several GDI cells.

## A. XOR Gate based on GDI Method

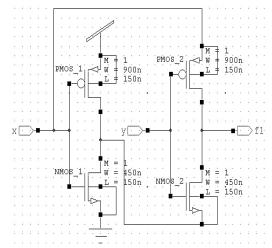

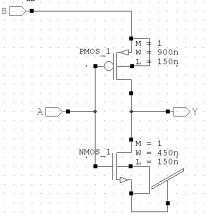

Fig. 3 shows the design of a XOR gate based on GDI procedure. It contains two GDI cells in which the first cell acts as a basic inverter while for the second cell 'x' is given as an input to port P of the GDI cell whereas 'y' is given as an input to port G and the output of the first cell is given as an input to port N of the second cell.

Fig. 3. the input and output waveforms of a XOR gate designed using GDI technique in 150nm technology.

#### **B. AND Gate based on GDI method**

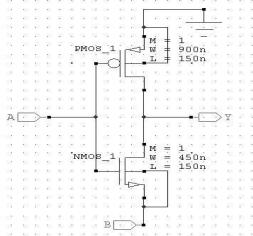

Fig. 4 shows the design of an AND gate based on GDI method. It requires a single GDI cell in which the source of the PMOS that is port P is connected to GND and A is given as an input to port G while port N is supplied input B.

International Journal of VLSI System Design and Communication Systems Volume.04, IssueNo.05, May-2016, Pages: 0332-0336

(2)

# Full Subtractor Design of Energy Efficient, Low Power Dissipation Using GDI Technique

Fig. 4. AND gate using GDI method.

## C. OR Gate based on GDI method

The OR gate consists of a single GDI cell as shown in Fig.5 where port P is given an input B, port G an input A while port N is supplied with  $V_{dd}$ .

Fig. 5. OR gate using GDI method.

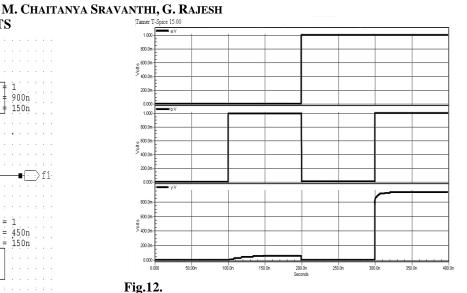

# D. NOT Gate based on GDI Method

The design of the NOT gate based on GDI procedure is similar to that of a standard CMOS inverter which is quite evident from table I. Fig.6 shows the circuit diagram of a NOT gate derived using GDI technique.

Fig.6. NOT gate using GDI method.

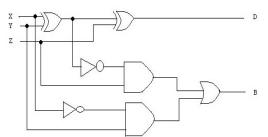

**IV. DESIGN OF THE PROPOSED FULL SUBTRACTOR** A full subtractor is a combinational circuit which performs subtraction on 3 bits that is minuend bit, subtrahend bit and the borrow bit from the previous stage. Therefore, a subtractor has 3 inputs– X (minuend), Y (subtrahend) and Z (Borrow from previous stage), and 2 outputs– D (difference) and B (Borrow out). The truth table for the full subtractor is displayed in table II.

| <b>TABLE II:</b> | Truth | Table of | a Full | Subtractor |

|------------------|-------|----------|--------|------------|

|------------------|-------|----------|--------|------------|

| Х | Y | Z | D | В |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Where D denotes difference and B represents the borrow. In the current paper, we propose the design of the full subtractor using GDI technique which will consume lesser power, exhibit higher speed thereby delivering a better power delay product along with a reduced transistor count. The design of the AND, XOR, OR and NOT gates using GDI procedure has already been discussed in section III. Using these logic gates, we propose a new circuit design of the full subtractor. The logic circuit of the full subtractor is shown in Fig. 7.

Fig.7.Logic Circuit of full subtractor.

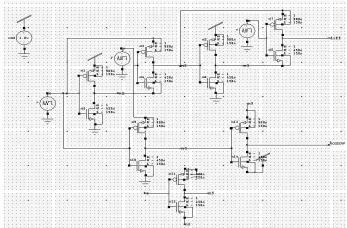

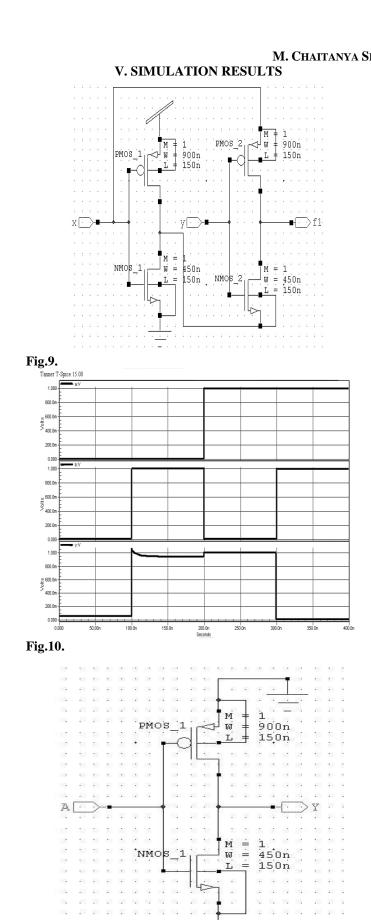

The circuit diagram of the proposed full subtractor is shown in Fig. 7 while fig. 8 depicts the corresponding layout design. The W/L ratio of all PMOS transistors is taken to be 6/1 whereas the W/L ratio of all NMOS transistors is taken to be 3/1.

Fig. 8Circuit diagram of the proposed full subtractor.

International Journal of VLSI System Design and Communication Systems Volume.04, IssueNo.05, May-2016, Pages: 0332-0336

B

# VI. CONCLUSION

The current work proposes the design of a full subtractor using Gate Diffusion Input (GDI) procedure which on simulation has been found to consume low power in conjunction with lesser delay time and fewer transistors while maintaining proper output-voltage swing. In order to establish the technology independence the present work has been performed in 150nm technology using Tanner SPICE and the layout has been concocted in Microwind. Comparisons with standard CMOS, transmission gate and CPL techniques showed a reduction of 72.00%, 63.16% and 58.82% in terms of transistor count, 99.68%, 88.78% and 99.99% in terms of average power consumption, 84.85%, 84.39% and 85.68% in terms of delay time and a significant 99.95%, 98.25 % and 99.99% in terms of power delay product, respectively. Furthermore, a depreciation of 97.24%, 92.42% together with 95.10% in surface area is reaped when judged against a full subtractor composed adopting the popular CMOS approach, transmission gates and CPL, proportionately. Because of the noteworthy minimization of power delay product, transistor count and surface area the proposed logic can be useful in portable and low power applications.

#### **VII. REFERENCES**

S Salivahanan and S Arivazhagan, "Digital Circuits and Design", 3<sup>rd</sup> ed., Vikas Publishing House Pvt Ltd., pp. 184-186

Maurus Cappa and V. Carl Hamacher, "An Augmented Iterative Array for High-Speed Binary Division", IEEE Transaction on computers, vol.c-22, no.–2, February 1973

[3] A. Morgenshtein, A. Fish, I. A. Wagner, "Gate Diffusion Input (GDI) –A Novel Power Efficient Method for Digital Circuits: A Design Methodology", 14th ASIC/SOC Conference, Washington D.C., USA, September 2001

[4] N. Weste and K. Eshraghian, Principles of CMOS digital design. Reading, MA: Addison-Wesley, pp. 304–307.

[5] A. P. Chandrakasan, S. Sheng, and R. W. Brodersen, "Lowpower CMOS digital design," IEEE J. Solid-State Circuits, vol. 27, pp. 473–484, Apr. 1992.

[6] A. P. Chandrakasan and R.W. Brodersen, "Minimizing power consumption in digital CMOS circuits," Proc. IEEE, vol. 83, pp. 498–523, Apr. 1995.

Fig.11.

International Journal of VLSI System Design and Communication Systems Volume.04, IssueNo.05, May-2016, Pages: 0332-0336

[7] Sung-Mo Kang and Yusuf Leblebici, CMOS Digital Integrated Circuits- Analysis and Design, 3rd ed., Tata Mc Graw-Hill ed., pp. 115-129, 211-214

[8] J. Rabaey, "Low Power Design Essentials", Springer, 2009

[9] K. Roy, S. Prasad, "Low-Power CMOS VLSI Circuit Design", Wiley India, 2009

[10] B. Calhoun, Y. Cao, X. Li, K. Mai, L. Pileggi, R. Rutenbar, K. Shepard, "Digital Circuit Design Challenges and Opportunities in the Era of Nanoscale CMOS", Proceedings of the IEEE, Vol. 96, Issue 2, pp. 343-365, Feb. 2008.